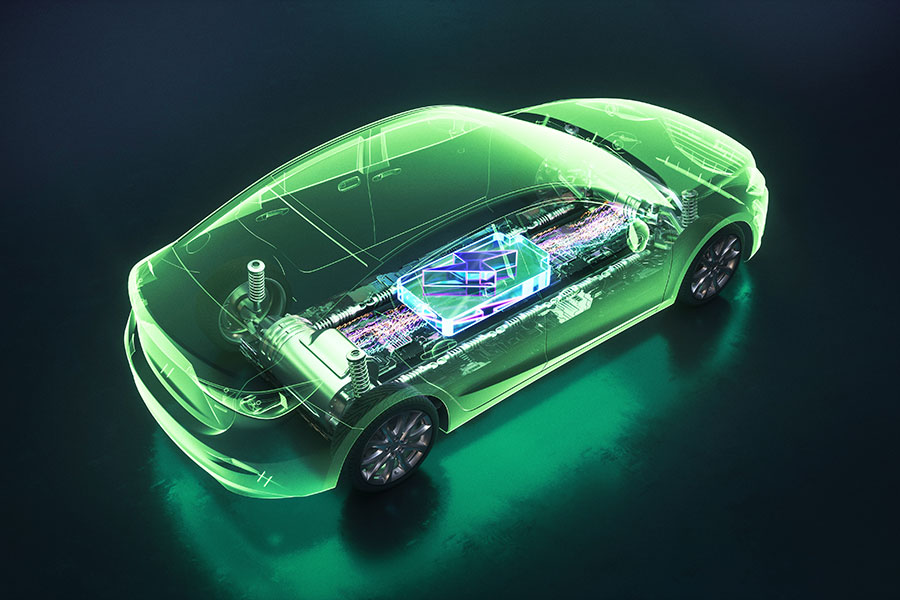

imec推动7埃米制程 提出双列CFET结构。(图:imec提供)

比利时微电子研究中心 (imec) 本周在 2024 年 IEEE 国际电子会议 (IEDM) 中,发表基于互补式场效电晶体 (CFET) 的全新标准单元结构,内含两列 CFET 元件,两列间共用一层讯号布线墙,可在 7 埃米 (A7) 逻辑节点提供权衡可制造性和面积效率的最佳取舍。

imec 指出,双列 CFET 架构的主要好处在于简化制程和大幅减少逻辑元件和静态随机存取存储器 (SRAM) 的面积,根据进行的设计技术协同优化 (DTCO) 研究,与传统的单列 CFET 相比,此新架构能让标准单元高度从 4 轨降到 3.5 轨。

目前半导体业在制造 (单片)CFET 元件方面持续获得重大进展,这些元件预计会在逻辑技术的发展历程中接替环绕闸极 (GAA) 纳米片架构。n 型和 p 型场效电晶体 (FET) 的元件堆叠在结合晶背供电和讯号布线技术后,可望带来功率、性能和面积 (PPA) 方面的优势。

然而,在电路层面,目前还有把 CFET 整合到标准单元的几种技术方案,用来维持甚至是强化预期的 PPA 优势。特别极具挑战的是中段制程的连接性,也就是把源极/汲极和闸极接点连接到 (晶圆背面和正面) 第一金属导线层的内连导线,以确保从元件顶层到底层具备功率和讯号传输的连接性。

imec 说,此新架构以一个基础单元为开端,该 CFET 单元内的一侧针对功率连接进行优化,包含一条把功率从晶背传输到顶层元件的电源轨 (接地电压 Vss),以及一条用于底层元件的直接晶背连接。

该 CFET 的另一侧则为讯号连接进行优化,方法是提供一层中间布线墙 (middle routing wall) 来连接元件顶层到底层。接着,利用反射制出两个这种基础单元,形成双列 CFET 标准单元 (包含两列堆叠元件),这两个单元共用同一个中间布线墙来进行讯号连接。

imec 设计技术协同优化 (DTCO) 研究计划主持人 Geert Hellings 表示,设计技术协同优化 (DTCO) 研究显示每 3.7 个场效电晶体共用一个中间布线墙就足以建立逻辑和 SRAM 单元。比起“传统的”单列 CFET,这能让我们进一步缩短标准单元高度,从 4 轨降到 3.5 轨。

对 SRAM 单元来说,这代表着面积大幅缩小了 15%。与像是 14 埃米 (A14) 纳米片技术制成的 SRAM 相较,双列 CFET 型的 SRAM 可以实现超过 40% 的面积缩减,持续推进 SRAM 的微缩之路。

这种双列 CFET 也能带来制程的简化,因为两列 CFET 元件之间共用一条中间布线墙的沟槽。如有必要连接顶层和底层元件,这种双列 CFET 免除了形成极高深宽比通道的需求,进而减少中段制程的流程复杂度和成本。

Geert Hellings 补充,从 7 纳米的技术节点开始,除了传统的元件微缩,运用设计技术协同优化 (DTCO) 来进行标准单元最佳化对于不同技术节点的微缩密度升级来说越来越重要。在我们为 CFET 架构进行的设计技术协同优化 (DTCO) 研究中,先设想未来 CFET 晶圆厂的制程能力,以确保实现可与产业接轨的制造流程。

透过在 imec 的 12 吋晶圆无尘室进行技术概念验证,也验研究中心的虚拟晶圆厂概念。这种结合虚拟晶圆厂和真实试验制程活动的做法,对推进技术发展来说至关重要。

因此,imec 也在 IEEE 国际电子会议 (IEDM) 透过实验展示了这种双列 CFET 架构的一个关键组件,即一颗功能性单片 CFET,该元件具备直接连接到底部 pMOS 元件源极/汲极的晶背接点。我们利用极紫外光 (EUV) 晶背图形化技术实现了这点,该图形化技术确保了晶背的功率和讯号布线稠密,还能紧密叠对 (精度小于 3 纳米) 晶圆正面制成的源极/汲极与晶背接点和后续的晶背金属层。